Olá a todos,

Meus caros, estou querendo implementar um buffer circular com uma saída serial comum (0~5v) start / stop, o tamanho do frame seria 20 caracteres.

Alguém poderia me dar uma luz.

Tanto faz assembler ou c...o micro que estou querendo usar é o pic18.

O objetivo da minha questão é polemizar o uso, atualmente eu já utilizo esse tipo de buffer com chamadas aleatórias dentro do MAIN, sem o uso de interrupções...

Obrigado,

BUFFER CIRCULAR???

Moderadores: andre_luis, 51, guest2003, Renie

4 mensagens

• Página 1 de 1

BUFFER CIRCULAR???

VonNilmam "Assembler" e agora "C"

-

Vonnilmam - Byte

- Mensagens: 446

- Registrado em: 19 Out 2006 14:25

- Localização: espacial

Re: BUFFER CIRCULAR???

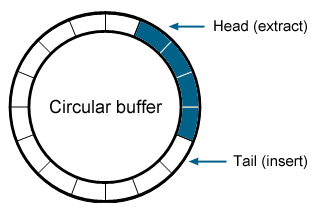

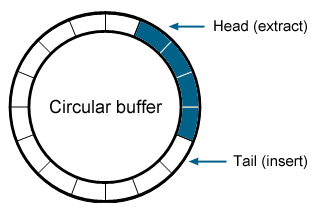

jah vi bastante em controladores ethernet... mas um ring buffer com elementos diretamente enderecaveis nao seria na realidade uma FIFO?

se o numero de elementos na FIFO for 2^n, fica melhor ainda, pois vc pode usar um pointeiro que possui n+1 bits e usar o bit extra para detectar quando a FIFO esta cheia ou vazia:

isso em verilog onde manipulamos bits diretamente, mas eh facilmente adaptavel para C ou asm com operadores logicos! no caso de FIFOs para apliacoes de alta performance, eh comum ainda detectores para a FIFO 1/4 cheia, 1/2 cheia ou 3/4 cheia, de modo a mudar a estrategia de operacao e maximizar a performance (ele acelera e desacelera a logica o uso para tentar manter a FIFO sempre em uso).

e de fato, usar frames nao muda muito o funcionamento... a diferenca eh que vc vai construir uma FIFO de pointeiros para frames e os frames entao vao aparecer em uma estrutura logica que eh o ring buffer! ou seja, a task prepara um frame e entao insere o pointeiro para o frame na lista. a medida que o controlador transmite os frames, ele vai tirando os ponteiros da FIFO... bem simples e eficiente! (:

evidentemente, vc pode construir listas linkadas para esse tipo de estrutura tambem, mas ring buffers sao mais facilmente manipulados por hardware puro (vide o exemplo de FIFO acima em verilog), motivo pelo qual ainda se usa muito para IO isso.

se o numero de elementos na FIFO for 2^n, fica melhor ainda, pois vc pode usar um pointeiro que possui n+1 bits e usar o bit extra para detectar quando a FIFO esta cheia ou vazia:

isso em verilog onde manipulamos bits diretamente, mas eh facilmente adaptavel para C ou asm com operadores logicos! no caso de FIFOs para apliacoes de alta performance, eh comum ainda detectores para a FIFO 1/4 cheia, 1/2 cheia ou 3/4 cheia, de modo a mudar a estrategia de operacao e maximizar a performance (ele acelera e desacelera a logica o uso para tentar manter a FIFO sempre em uso).

e de fato, usar frames nao muda muito o funcionamento... a diferenca eh que vc vai construir uma FIFO de pointeiros para frames e os frames entao vao aparecer em uma estrutura logica que eh o ring buffer! ou seja, a task prepara um frame e entao insere o pointeiro para o frame na lista. a medida que o controlador transmite os frames, ele vai tirando os ponteiros da FIFO... bem simples e eficiente! (:

evidentemente, vc pode construir listas linkadas para esse tipo de estrutura tambem, mas ring buffers sao mais facilmente manipulados por hardware puro (vide o exemplo de FIFO acima em verilog), motivo pelo qual ainda se usa muito para IO isso.

Vonnilmam escreveu:Olá a todos,

Meus caros, estou querendo implementar um buffer circular com uma saída serial comum (0~5v) start / stop, o tamanho do frame seria 20 caracteres.

Alguém poderia me dar uma luz.

Tanto faz assembler ou c...o micro que estou querendo usar é o pic18.

O objetivo da minha questão é polemizar o uso, atualmente eu já utilizo esse tipo de buffer com chamadas aleatórias dentro do MAIN, sem o uso de interrupções...

Obrigado,

-

msamsoniuk - Dword

- Mensagens: 2935

- Registrado em: 13 Out 2006 18:04

Re: BUFFER CIRCULAR???

Olha, nunca havia pensado sobre um buffer circular endereçado ser ou não uma FIFO... Mas como realmente o efeito "primeiro que entra" eh o "primeiro que sai" acho que poderia ser categorizado como uma "FIFO sem fim". Kkkk!

Isso de detectar se o buffer está cheio não faz muito sentido porque o propósito de uma topologia circular eh justamente não precisar ter um buffer maior ou igual ao pacote de dados que você vai receber. Por isso que controladores de Ethernet usam muito isso!

Particularmente eu uso buffer circular para tudo (ou quase tudo)! A proposta eh, se o microcontrolador consegue processar no laço principal os dados recebidos mais rápido do que estão chegando (o que com certeza ocorre em uma porta serial) então seu buffer pode ser menor que o pacote de dados! Com um buffer circular de 20bytes (para o caso do amigo que iniciou o post) você pode receber grandes pacotes de 256bytes, de 1024, e etc.... A única condição exigida eh que o microcontrolador consiga processar os dados antes de uma sobreposição dos dados.

Um exemplo simples:

cpp code

Eh isso! Espero ter ajudado!

Enviado do meu iPhone usando Tapatalk

Isso de detectar se o buffer está cheio não faz muito sentido porque o propósito de uma topologia circular eh justamente não precisar ter um buffer maior ou igual ao pacote de dados que você vai receber. Por isso que controladores de Ethernet usam muito isso!

Particularmente eu uso buffer circular para tudo (ou quase tudo)! A proposta eh, se o microcontrolador consegue processar no laço principal os dados recebidos mais rápido do que estão chegando (o que com certeza ocorre em uma porta serial) então seu buffer pode ser menor que o pacote de dados! Com um buffer circular de 20bytes (para o caso do amigo que iniciou o post) você pode receber grandes pacotes de 256bytes, de 1024, e etc.... A única condição exigida eh que o microcontrolador consiga processar os dados antes de uma sobreposição dos dados.

Um exemplo simples:

cpp code

SHORT RxPop=0;

SHORT RxPush=0;

BYTE RxBuf[20];

void interrupt U1RxData(void)

{

If( RxPush >= sizeof(RxBuf) ) RxPush = 0;

RxBuf[RxPush++] = RXBUF;

}

Eh isso! Espero ter ajudado!

Enviado do meu iPhone usando Tapatalk

/***************************************

Rafael Gebert

TEWAC Tecnologia

e-mail: rafael@tewac.com.br

***************************************/

Rafael Gebert

TEWAC Tecnologia

e-mail: rafael@tewac.com.br

***************************************/

- rafael

- Nibble

- Mensagens: 70

- Registrado em: 08 Mar 2007 10:37

- Localização: Rio Grande, RS - Brazil

Re: BUFFER CIRCULAR???

Então, eu agradeço a colaboração inteligente dos amigos.

Realmente as duas idéias são muito interessantes, parabéns.

Em um projeto novo, onde já utilizo a muitos anos a mesma rotina "main" e seus drivers, houve a necessidade de aumentar o número de dados circulando dentro do "buffer circular", isso trouxe, devido ao aumento do buffer, um atraso considerável para descarregar os dados na serial TX...esse atraso, foi devido ao grande número de bytes enviados pelo buffer à tx.

Então depois ao invés de enviar um "frame" completo que estava no buffer circular, fazendo assim um certo congestionamento, transtornando a tx, resolvi enviar um byte de cada vez para a tx, pela ordem do buffer.

O resultado foi que a rotina voltou a ficar veloz, pois os dados cavalares contidos no buffer, foram enviados um a um para a tx, sem congestionar o fluxo do main.

Todas as dicas são muito boas, para uso em programas simples até mais complexos, onde a velocidade é importante e o micro não é lá muito essas coisas.

Exemplo do que fiz: "não usei interrupção alguma para esse feito no buffer circular".

Dentro da rotina main coloquei simplesmente bits de sinalização para cada elemento do buffer e através de um bit sinalização que era disparado apenas quando havia necessidade de ler ou escrever um dado na serial, assim o buffer era descarregado sequencialmente para as seriais.

Realmente as duas idéias são muito interessantes, parabéns.

Em um projeto novo, onde já utilizo a muitos anos a mesma rotina "main" e seus drivers, houve a necessidade de aumentar o número de dados circulando dentro do "buffer circular", isso trouxe, devido ao aumento do buffer, um atraso considerável para descarregar os dados na serial TX...esse atraso, foi devido ao grande número de bytes enviados pelo buffer à tx.

Então depois ao invés de enviar um "frame" completo que estava no buffer circular, fazendo assim um certo congestionamento, transtornando a tx, resolvi enviar um byte de cada vez para a tx, pela ordem do buffer.

O resultado foi que a rotina voltou a ficar veloz, pois os dados cavalares contidos no buffer, foram enviados um a um para a tx, sem congestionar o fluxo do main.

Todas as dicas são muito boas, para uso em programas simples até mais complexos, onde a velocidade é importante e o micro não é lá muito essas coisas.

Exemplo do que fiz: "não usei interrupção alguma para esse feito no buffer circular".

Dentro da rotina main coloquei simplesmente bits de sinalização para cada elemento do buffer e através de um bit sinalização que era disparado apenas quando havia necessidade de ler ou escrever um dado na serial, assim o buffer era descarregado sequencialmente para as seriais.

VonNilmam "Assembler" e agora "C"

-

Vonnilmam - Byte

- Mensagens: 446

- Registrado em: 19 Out 2006 14:25

- Localização: espacial

4 mensagens

• Página 1 de 1

Quem está online

Usuários navegando neste fórum: Nenhum usuário registrado e 1 visitante