pois eh, tem um fundo de fato e ficcao nessa historia... o fato eh que essa historia de multiplas fases de clock existe, porem ela eh bem antiga.

lah nos primordios da decada de 70, o 8080 usava dois clocks assimetricos:

nao tenho muita certeza de como funciona: aparentemente eles usam a borda positiva de Φ1 e de Φ2, que sao distintas, mas as bordas negativas sao coincidentes. assim daria para gerar no maximo 3 estados distintos por clock... se for 3 estados distintos por clock de 2MHz, seria equivalente a 6MHz. mas acredito que sao apenas 2 estados por clock, o que seria equivalente a 4MHz. nao lembro muito sobre a capacidade de execucao: aparentemente ele requer pelo menos 4 clocks TTL por instrucao, o que daria 1 MNOP/s (milhoes de NOPs por segundo).

detalhes sinistros: pelas indicacoes de TΦ1 e TΦ2 eh de se pensar: se forem 2 estados, entao o tempo de propagacao flip-flop/flip-flop eh a soma dos tempos. se forem 3 estados, entao sao tempos distintos: 2 saltos de estados sao com TΦ1 e um com TΦ2.

o 6501, da mesma epoca, tambem usava dois clocks assimetricos:

aparentemente, nenhuma das bordas eh coincidente, entao daria para usar tanto a borda positiva quanto negativa de Φ1 e de Φ2, gerando 4 estados distintos por clock. para um clock de 2MHz, os 4 estados distintos seriam equivalentes a um clock de 8MHz. como possui duas vezes mais estados por clock, a performance teorica seria de 2 MNOP/s.

detalhe sinistro: os valores de PWHΦ1 e PWHΦ2 sao bem bons, quase 1/2 periodo do oscilador... mas TD eh incrivelmente curto. o bom senso indica que deveria ter apenas 2 estados por clock...

bom, o 6502 possui um unico clock, porem tem uma maracutaia: ele gera a outra fase internamente. assim, se vc imaginar que o clock abaixo eh Φ2 e inferir o clock Φ1 segundo a relacao acima, podemos facilmente verificar alguns estados distintos correspondentes a Φ1:

detalhe sinistro: embora o bom senso indique 2 estados por clock, nitidamente o desenho mostra em suas operacoes de read/write pelo menos 3 estados diferentes por clock. eu dei uma fucada em datasheets antigos e os diagramas de bus mostram claramente 3 estados/clock... nos diagramas do 65C816, que eh mais moderno, nitidamente parece existir 4 estados por clock. acho que nunca vou conseguir descobrir...

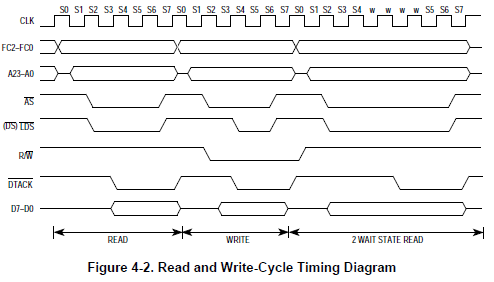

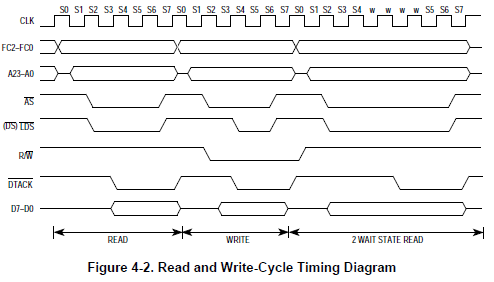

bom, na decada de 80, porem, a maioria dos processadores usava um unico clock e dois estados por clock, como no caso do 68000:

se fosse comparar com os outros, a 2MHz, seria equivalente a 4MHz apenas. mas trata-se de um componente muito mais moderno: para um clock tipico de 16MHz, a capacidade com dois estados por clock jah seria equivalente a 32MHz. porem ele usa 8 estados por instrucao, o que limita a performance em 4MNOP/s.

o pulo do gato eh justamente esse: se vc diminuir a quantidade de clocks, vc consegue aumentar o clock. e na decada de 90 comecaram a surgir processadores trabalhando com uma unica borda de clock, como por exemplo, o 68040:

neste caso, se fosse comparar com os 2MHz dos circuitos antigos, a performance efetiva seria de apenas 2MHz realmente. mas trabalhando com uma unica borda de clock esse componente consegue rodar a 40MHz. e a evolucao tecnologica eh notavel tambem na quantidade de estados por instrucao: 1 estado por instrucao, ou seja, performance de 40MNOP/s.

a historia nao acaba por aih: ainda na decada de 90 surgiram processadores super-escalares, vetoriais, etc. mas daih jah eh outra historia.

o fato eh que, conhecendo essa breve historia, dah para concluir que aquela historia do AVR tem um fundo de fato e um fundo de mito:: a tecnica existe e foi usada no passado, mas o AVR eh da decada de 90 e me parece bem improvavel que utilize multiplos estados por clock ou multiplas fases de clock. muita gente ainda prega as vantagens do 6502 hoje em dia, mas o fato eh que o 6502 eh "bad design": seria o mesmo que querer ressussitar o fusca. foi legal em sua epoca, mas passou. de fato, eh citado sempre que se trata de um RISC classico, com pipeline simples de dois estagios. mas como eh fechado, nao existem muitos detalhes...

bom, nao temos como fucar nas entranhas do AVR, mas dah para ilustrar como funciona:

https://darklife.org/marcelo/public/xilinx/src/core.veste eh o codigo de um pequeno processador RISC que eu projetei em um final de semana qualquer para finalidades didaticas: malemal possui 100 linhas de codigo verilog, ocupa 1/3 de uma FPGA pequena de 5 obamas, possui 16 registros de 16 bits, roda tranquilamente a 80MHz e roda deterministicamente todas as instrucoes em apenas um clock, incluindo a instrucao de mutiplicacao 16x16 com shift integrado. como a ROM eh armazenada em blockram e ela requer um clock para leitura, acaba ficando implicito o pipeline simples de dois estagios (busca/executa), muito similar ao que li por aih do AVR. um fato importante: ele consegue atingir a casa dos 80MIPs justamente pq roda com uma unica borda de clock.

bom, estudando esse processador simples, dah para perceber a essencia do negocio: suponha que vc tem um par de flip-flops e entre eles tenha uma certa logica combinacional que consome um tempo t (por exemplo, o multiplicador de 16x16 bits). esse tempo t determina o periodo do seu clock, de modo que, quando o clock registra uma entrada no primeiro flip-flop, a saida que muda passa pela logica combinacional com delay t a tempo de ser registrado pelo segundo flip-flop. se vc usar duas fases, vc pode ter uma fase no primeiro flip-flop e outra fase no segundo. mas o tempo t de propagacao nao muda: assim, vc vai ter um tempo t entre uma fase e outra, portanto o periodo tem que ser 2t. assim aquele processador que rodava a 80MHz acaba tendo que rodar a 40MHz, ou seja, um desastre completo! talvez seja possivel adicionar pipelines extras e tentar compensar essa perda, mas o projeto comeca a complicar para, aparentemente, atingir exatamente o mesmo resultado que jah tinha antes. se eh para adicionar pipelines e complicar, seria mais interessante entao manter uma borda unica e partir para algo acima dos 80MHz. de fato, com pipelines, acredito que seja possivel atingir os 160MHz com facilidade. projetinho de fim de semana, usando talhadeira e martelo aqui na garagem! francamente, nao sei qual seria a dificuldade e/ou custos para a atmel ou qq outro projetar processadores melhores do que isso. ou talvez sejam apenas uma fachada para produtos chineses de baixa qualidade, sei lah.

bom, a conclusao eh que eu diria entao que parece bastante improvavel que o AVR use multiplas fases de clock. nao eh impossivel, afinal o 68000 continua sendo fabricado como era em 1979, usando duas bordas de clock... eles apenas fizeram um xerox dos filmes com uma reducao de 50% para aproveitar rebarbas das bolachas de silicio onde fabricam os powerpcs, daih os 68000 atuais andam rodando 4x mais rapido do que o datasheet indicam hehehe mas fora isso, eh o mesmo chip da decada de 80... o AVR eh muito mais moderno, parece dificil acreditar que alguem iria abrir um portal dimensional e trazer projetistas da decada de 70 para fazer algo do genero. entao eu acho que essa historia aih nao passa de ficcao!

de forma similar, a escolha para o arduino me parece muito mais acidental do que intencional: nao me parece existir absolutamente nenhum motivo especial para a escolha dele.