RISC V

Moderadores: andre_luis, 51, guest2003, Renie

39 mensagens

• Página 1 de 3 • 1, 2, 3

RISC V

Já começou a aparecer placa com RISC V a preço razoável,

https://www.cnx-software.com/2019/08/29 ... enclosure/

alguém aqui (além do Marcelo que implementou RISC V em FPGA) tem lidado com RISC-V ou se interessado?

Mesmo com o dolar nas alturas estou inclinado a comprar uma Longan Nanon só pra experimentar.

https://www.cnx-software.com/2019/08/29 ... enclosure/

alguém aqui (além do Marcelo que implementou RISC V em FPGA) tem lidado com RISC-V ou se interessado?

Mesmo com o dolar nas alturas estou inclinado a comprar uma Longan Nanon só pra experimentar.

- pamv

- Word

- Mensagens: 842

- Registrado em: 20 Jun 2016 21:47

Re: RISC V

verdade, o Marcelo havia implementado!

------------------------------------------

http://www.youtube.com/tcpipchip

http://www.youtube.com/tcpipchip

-

tcpipchip - Dword

- Mensagens: 6561

- Registrado em: 11 Out 2006 22:32

- Localização: TCPIPCHIPizinho!

Re: RISC V

pamv escreveu:Já começou a aparecer placa com RISC V a preço razoável,

https://www.cnx-software.com/2019/08/29 ... enclosure/

alguém aqui (além do Marcelo que implementou RISC V em FPGA) tem lidado com RISC-V ou se interessado?

Mesmo com o dolar nas alturas estou inclinado a comprar uma Longan Nanon só pra experimentar.

Com essa onda de Cortex M0, M3, M4... , o que faz você procurar por um RISC?

Eu abri o link, os caras são bem ousados, aparentemente "criaram" um nome parecido com o STM32F103 mas chamaram de GD32VF103.

- denis

- Byte

- Mensagens: 257

- Registrado em: 06 Mar 2007 12:29

- Localização: Americana - SP

Re: RISC V

denis escreveu:pamv escreveu:Já começou a aparecer placa com RISC V a preço razoável,

https://www.cnx-software.com/2019/08/29 ... enclosure/

alguém aqui (além do Marcelo que implementou RISC V em FPGA) tem lidado com RISC-V ou se interessado?

Mesmo com o dolar nas alturas estou inclinado a comprar uma Longan Nanon só pra experimentar.

Com essa onda de Cortex M0, M3, M4... , o que faz você procurar por um RISC?

Eu abri o link, os caras são bem ousados, aparentemente "criaram" um nome parecido com o STM32F103 mas chamaram de GD32VF103.

Você já leu sobre o RISC V?

https://riscv.org/

RISC-V is a free and open ISA enabling a new era of processor innovation through open standard collaboration. Born in academia and research, RISC-V ISA delivers a new level of free, extensible software and hardware freedom on architecture, paving the way for the next 50 years of computing design and innovation.

- pamv

- Word

- Mensagens: 842

- Registrado em: 20 Jun 2016 21:47

Re: RISC V

tcpipchip escreveu:verdade, o Marcelo havia implementado!

E o pessoal do Litex também anda lidando com o RISC V

https://github.com/timvideos/litex-buil ... -CPU#linux

- pamv

- Word

- Mensagens: 842

- Registrado em: 20 Jun 2016 21:47

Re: RISC V

Vez ou outra eu vejo notícias de microcontroladores que estão sendo lançados com core Risc-V, há uma possibilidade de que em poucos anos este core se torne bastante popular, concorrendo diretamente com ARM.

Eu tenho curiosidade de conhecer mais a fundo este core, só me falta tempo...

Eu tenho curiosidade de conhecer mais a fundo este core, só me falta tempo...

98% das vezes estou certo, e não estou nem aí pros outros 3%.

-

xultz - Dword

- Mensagens: 3001

- Registrado em: 13 Out 2006 18:41

- Localização: Curitiba

Re: RISC V

xultz escreveu:Vez ou outra eu vejo notícias de microcontroladores que estão sendo lançados com core Risc-V, há uma possibilidade de que em poucos anos este core se torne bastante popular, concorrendo diretamente com ARM.

Eu tenho curiosidade de conhecer mais a fundo este core, só me falta tempo...

O problema é que muitos aqui,daqui uns anos,estará beirando os 60 anos...

-

vtrx - Dword

- Mensagens: 2240

- Registrado em: 20 Abr 2008 21:01

Re: RISC V

vtrx escreveu:xultz escreveu:Vez ou outra eu vejo notícias de microcontroladores que estão sendo lançados com core Risc-V, há uma possibilidade de que em poucos anos este core se torne bastante popular, concorrendo diretamente com ARM.

Eu tenho curiosidade de conhecer mais a fundo este core, só me falta tempo...

O problema é que muitos aqui,daqui uns anos,estará beirando os 60 anos...

E nenhum desses estará aposentado ainda e nem será um milionário a viver de rendas, então a idade não é um problema

- pamv

- Word

- Mensagens: 842

- Registrado em: 20 Jun 2016 21:47

Re: RISC V

obrigado por me acordarem do sono eterno! de fato, fazia tempo que nao postava nada pq eu estava recluso em uma cruzada epica contra os interminaveis exercitos de ARMs que tentam a todo custo conquistar as terras sagradas dos antigos ancestrais 680x0 e coldfire:

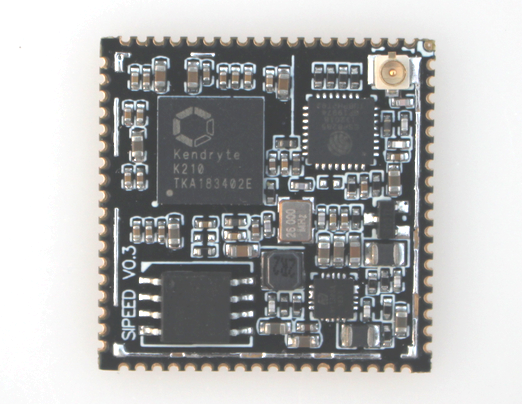

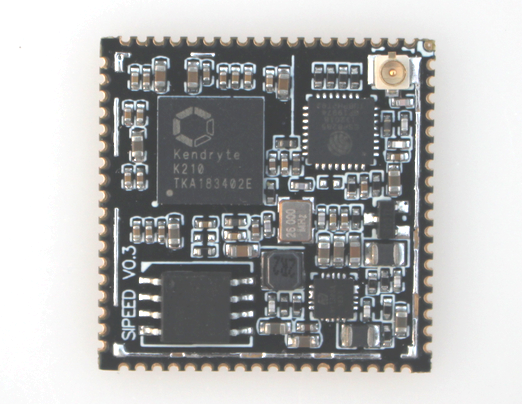

na sexta-feira coloquei mais um RISCV no ar em uma FPGA e jah consigo ateh fazer uma pausa para tomar um banho, trocar as roupas sujas com o sangue dos ARMs inimigos e ler um e outro post antes de retonar para outra batalha sangrenta na segunda-feira... o fato de estarem fazendo manutecao no no-break do trampo tb indica que nao tem absolutamente nenhuma forma de trampar fim de semana! bom, se a placa do chines eh boa ou nao, eu nao sei, bem pq fora de FPGA nao sei como RISCV esta indo... eu cheguei a comprar uma speed m1w, que eh tipo uma esp32 killer, mas nao tive tempo de mexer com ela:

https://www.indiegogo.com/projects/sipe ... -ai-module

paguei uns 10USD na aliexpress.com e ela vem com um dual-RV64IMAFDC de 400MHz (rola overclock ateh 800MHz), 64 KPUs de 576 bits (sabe deus o que seria isso) e 8MB de RAM on-chip! o tal do KPU eh para processamento de video e audio e atinge 230Gops/s segundo a propaganda! de quebra ela vem com um esp8285 (justamente o "w" da opcao m1w) e uma FLASH de 8MB ou qq coisa assim integrados no modulo, que eh pequeno, mas relativamente facil de manipular. infelizmente o tempo esta curto e nao acho que vou ter mto tempo para mexer nela... de qq forma, fica a dica: ela eh quase 20x mais rapida e tem mais de 200x mais memoria que o microcontrolador chines!

@xultz: nada de desculpa para nao aprender RISCV hein! jah tem ateh livro gratis:

http://riscvbook.com/portuguese/

talvez o RISCV demore um bom tempo para emplacar no ocidente, mas eh fato que lah no oriente o ARM jah esta praticamente morto por conta da guerra comercial com o ocidente e todo mundo pr lah esta migrando em massa para RISCV. o povo do MIPS e POWER jah se ligaram nisso e comecaram a liberar tudo free para tentar pular por cima da guerra comercial, mas na minha opiniao demoraram muito e agora eh questao dos presuntos esfriarem, pq jah estao todos mortos! e os proximos serao o ARM e x86! huahuahua

huahuahua

na sexta-feira coloquei mais um RISCV no ar em uma FPGA e jah consigo ateh fazer uma pausa para tomar um banho, trocar as roupas sujas com o sangue dos ARMs inimigos e ler um e outro post antes de retonar para outra batalha sangrenta na segunda-feira... o fato de estarem fazendo manutecao no no-break do trampo tb indica que nao tem absolutamente nenhuma forma de trampar fim de semana! bom, se a placa do chines eh boa ou nao, eu nao sei, bem pq fora de FPGA nao sei como RISCV esta indo... eu cheguei a comprar uma speed m1w, que eh tipo uma esp32 killer, mas nao tive tempo de mexer com ela:

https://www.indiegogo.com/projects/sipe ... -ai-module

paguei uns 10USD na aliexpress.com e ela vem com um dual-RV64IMAFDC de 400MHz (rola overclock ateh 800MHz), 64 KPUs de 576 bits (sabe deus o que seria isso) e 8MB de RAM on-chip! o tal do KPU eh para processamento de video e audio e atinge 230Gops/s segundo a propaganda! de quebra ela vem com um esp8285 (justamente o "w" da opcao m1w) e uma FLASH de 8MB ou qq coisa assim integrados no modulo, que eh pequeno, mas relativamente facil de manipular. infelizmente o tempo esta curto e nao acho que vou ter mto tempo para mexer nela... de qq forma, fica a dica: ela eh quase 20x mais rapida e tem mais de 200x mais memoria que o microcontrolador chines!

@xultz: nada de desculpa para nao aprender RISCV hein! jah tem ateh livro gratis:

http://riscvbook.com/portuguese/

talvez o RISCV demore um bom tempo para emplacar no ocidente, mas eh fato que lah no oriente o ARM jah esta praticamente morto por conta da guerra comercial com o ocidente e todo mundo pr lah esta migrando em massa para RISCV. o povo do MIPS e POWER jah se ligaram nisso e comecaram a liberar tudo free para tentar pular por cima da guerra comercial, mas na minha opiniao demoraram muito e agora eh questao dos presuntos esfriarem, pq jah estao todos mortos! e os proximos serao o ARM e x86!

-

msamsoniuk - Dword

- Mensagens: 2935

- Registrado em: 13 Out 2006 18:04

Re: RISC V

Bem vindo de volta Marcelo, tu tava sumido.

Esse módulo aí é legal, mas dependendo da aplicação ele num vai matar os ESP, tem ESP32 custando USD2,00

Esse módulo aí é legal, mas dependendo da aplicação ele num vai matar os ESP, tem ESP32 custando USD2,00

---

-

Rodrigo_P_A - Dword

- Mensagens: 2237

- Registrado em: 12 Out 2006 18:27

- Localização: Osasco - S.P - Brasil

Re: RISC V

Rodrigo_P_A escreveu:Bem vindo de volta Marcelo, tu tava sumido.

Esse módulo aí é legal, mas dependendo da aplicação ele num vai matar os ESP, tem ESP32 custando USD2,00

Eu acredito que esse aí para hobistas, para quem quiser experimentar com o RISC V e o ambiente de desenvolvimento. Quem tá investindo nele é a Alibaba e a Huawei

https://www.techrepublic.com/article/al ... for-5g-ai/

https://www.tomshardware.com/news/huawe ... 40238.html

- pamv

- Word

- Mensagens: 842

- Registrado em: 20 Jun 2016 21:47

Re: RISC V

Rodrigo_P_A escreveu:Bem vindo de volta Marcelo, tu tava sumido.

Esse módulo aí é legal, mas dependendo da aplicação ele num vai matar os ESP, tem ESP32 custando USD2,00

acho que o grande apelo de qq coisa que usa RISCV eh o fato do ISA e extensoes serem vastamente documentados, com disponibilidade de tools e ferramentas de debug bem padronizadas, que permitem elucidar melhor os problemas, bem como a troca de experiencias sobre o mesmo problema visto de diferentes variantes do mesmo ISA... em que pese isso ser um loop sem sentido, pq no fim das contas a sipeed m1w possui um esp no modulo e vc acaba dependente da espressif do mesmo jeito! hahaha

-

msamsoniuk - Dword

- Mensagens: 2935

- Registrado em: 13 Out 2006 18:04

Re: RISC V

Esse módulo que o Marcelo apresentou é muito legal e poderoso, pena que eu num posso me dedicar a estudar visão computacional , sempre quis e nunca tenho tempo.

Enviado do meu iPhone usando Tapatalk

Enviado do meu iPhone usando Tapatalk

---

-

Rodrigo_P_A - Dword

- Mensagens: 2237

- Registrado em: 12 Out 2006 18:27

- Localização: Osasco - S.P - Brasil

Re: RISC V

Legal, Sam, muito interessante saber que você está mexendo com isso, de quebra já responde a uma pergunta filosofal que vem sido feita há muitos e muitos séculos: esse trem desse Risc-V é bão mesmo?

Se você está se dedicando ao assunto, então é porque ele é sim. Deu até uma mega animada prá estudar e eventualmente fazer um deles piscar um led.

Se você está se dedicando ao assunto, então é porque ele é sim. Deu até uma mega animada prá estudar e eventualmente fazer um deles piscar um led.

98% das vezes estou certo, e não estou nem aí pros outros 3%.

-

xultz - Dword

- Mensagens: 3001

- Registrado em: 13 Out 2006 18:41

- Localização: Curitiba

Re: RISC V

xultz escreveu:Legal, Sam, muito interessante saber que você está mexendo com isso, de quebra já responde a uma pergunta filosofal que vem sido feita há muitos e muitos séculos: esse trem desse Risc-V é bão mesmo?

Se você está se dedicando ao assunto, então é porque ele é sim. Deu até uma mega animada prá estudar e eventualmente fazer um deles piscar um led.

entao, faz um anos que eu estou trabalhando com um soft-DSP proprietario de 16 bits em FPGA. apesar de eu mesmo ter comecado a ideia e desenvolvido varios cores similares, meu colega de trabalho foi a fundo escovando bits e conseguiu algo assombrosamente eficiente! comecamos substituindo DSPs discretos e foi evoluindo... no ultimo projeto que fiz ano passado, implementei uma stack IP em assembler capaz de suportar centenas de canais RTP na FPGA! apesar de ser 16 bits, um unico soft-DSP rodando a miseros 64MHz consegue segurar de boas o ping flood de um core2 duo de 2GHz. mas tem seus problemas... comeca com o assembler: nao eh exatamente um bicho de sete cabecas, mas certamente teria sido bem mais simples implementar em C! mas o problema eh que nosso soft-DSP proprietario nao tem compilador C: pesquisei sobre a possibilidade de portar e pareceu impossivel. fui pelo caminho contrario, que seria pegar algo suportado e tentar implementar, mas nao pareceu que ia ficar bom com nada que o compilador suporta:

https://www.gnu.org/software/gcc/backends.html

e nem entrei na questao de patentes: mexer no GCC provavelmente iria requerer liberar o codigo (licenca GPL). usar uma arquitetura existente poderia infrigir patentes dessa arquitetura, salvo as mais antigas cujas patentes expiraram (68000, por exemplo). um soft-68000 com suporte a GCC tem umas 3000LUTs, roda a uns 40MHz no maximo e tem performance maxima de uns 20MIPS. nao eh ruim se considerar que eh 10x melhor que um 68000 tipico, mas eh bem fraquinho comparativamente com outras opcoes modernas. eu nao consigo, por exemplo, tirar codigo de um DSP discreto legado e colocar nele... comparativamente, nosso soft-DSP proprietario tem 600LUTs, consegue atingir a 133MHz e roda ateh uns 1000MIPS se vc for muito bom em paralelizar e otimizar codigo em assembler.

bom, quando tudo parecia meio perdido, eu fiquei sabendo do RISCV... foi meio que por acidente, na epoca que saiu o meltdown e spectre para x86. e mesmo assim, demorou meses para cair a ficha e entender conceitualmente como o negocio funcionava. um ponto chave era a licenca BSD, que possui o melhor dos mundos aberto e corporativo: livre para usar, livre para mexer, livre para optar nao abrir seus codigos secretos. comecei a testar com o picorv32, que eh um core aberto relativamente compacto (~1000 LUTs) e veloz (~150MHz em uma spartan-6):

https://github.com/cliffordwolf/picorv32

compilei um cross-gcc para ele e magicamente funcionava!

infelizmente a implementacao nao era realmente tao boa quanto eu esperava: em 150MHz, ele rendia no maximo 50MIPS. fueh! mas pera, o RISCV define o set de instrucoes, nao a implementacao... e como eu jah tinha projetado outros processadores mais simples de 16 bits e conseguia uma boa relacao entre clock e performance, fui tirar a prova para ver se conseguia melhorar isso. um belo dia, partindo do zero, projetei um core RISCV que conseguia 75MIPS rodando em 75MHz. em uma noite! jah era uma melhoria de 50%, mas a vantagem maior era ter construido em torno de uma arquitetura de harvard e usar um conceito de bus mais eficiente, essencial para manter 1 clock/instrucao, ao menos operando dentro da FPGA.

bom, isso foi um ano atras e atualmente esse core consegue um maximo de 100MIPS em 100MHz na mesma spartan-6. ainda falta bastante coisa para poder substituir um 68000 ou coldfire, mas jah rola substituir DSPs e ter mais conforto colocando software embarcado em FPGA. e nesse meio tempo tambem rolaram varias coisas interessantes: surgiram novos cores RISCV para FPGAs e isso por si abalou as estruturas de licencas do ARM, MIPS e POWER!

os dois primeiros sao arquiteturas chuleh, mas o POWER come x86s no cafeh da manha e eh usado em supercomputadores:

https://www.networkworld.com/article/32 ... tml#slide1

do top 10, 3 usam POWER, incluindo os 2 primeiros. mas a coisa nao eh simples para estes caras nao... comparativamente, basta dizer que a primeira implementacao free do POWER (no momento a unica existente eh um POWER8) possui 11 mil LUTs, ou seja, consome 11x mais area que um RISCV tipico. nao que nao tenha RISCV grande, de fato os maiores talvez sejam 20x maiores que que eu projetei, mas tambem existem alguns muito menores, talvez com 1/4 do tamanho. pelo tamanho, suponho que nao passe de 40 ou 50MHz. enfim, da mesma forma, existem alguns ARMs e MIPSes que consomem seus respectivos espacos e nao eh pouco.

o ponto chave eh que existem muitos cores RISCV:

https://riscv.org/risc-v-cores/

ao inves de serem cores padroes como no caso do MIPS e ARM, ou entao de uma solucao pontual como no POWER, existe uma vasta variedade de cores RISCV que foram criados justamente pq os desenvolvedores originais nao acharam algo que batesse com seus requisitos. e isso eh apenas a primeira onda, ou seja, pessoal que partiu do zero e comecou a testar em FPGA, com performances entre 50 e 550MHz. enquanto eu coloco um RISCV rodando a 100MHz em uma FPGA, tem cara que tah lah na frente colocando 1800 RISCV rodando a 550MHz em uma FPGA:

https://twitter.com/jangray/status/1161314901500915712

e a medida que as tecnicas se refinam e se confirmam validas, a tendencia agora eh vir uma segunda onda justamente de cores amplamente testados em FPGA e implementados em ASICs, subindo a performance para 2.5GHz, caso dos chips anunciados pela hawei, western digital, nvidia e, quem diria, ateh mesmo a amada microchip do @fabim

https://www.electronicdesign.com/indust ... -mate-fpga

bom, no meu caso eh questao de sobrevivencia: jah trabalho em tempo integral com FPGAs, superei o desafio do DSP discreto, matei dezenas de ASICs e para ir adiante preciso superar a barreira do processador discreto e do compilador C. para o pessoal de microcontroladores e outras areas, a motivacao provavelmente eh menor. mas acho que independente da area, eh apenas uma questao de tempo para o RISCV chegar.

detalhe interessante: o primeiro chip feito de nanotubos de carbono eh um RISCV:

https://techreport.com/news/3465249/res ... nanotubes/

-

msamsoniuk - Dword

- Mensagens: 2935

- Registrado em: 13 Out 2006 18:04

39 mensagens

• Página 1 de 3 • 1, 2, 3

Quem está online

Usuários navegando neste fórum: Nenhum usuário registrado e 1 visitante